# TMC22091/TMC22191

# **Digital Video Encoders/Layering Engine**

### **Features**

- · All-digital video encoding

- · Internal digital oscillators, no crystals required

- Multiple input formats supported

- 24-bit and 15-bit GBR/RGB

- YCBCR422 or 444

- Color indexed

- 30 overlay colors (TMC22191)

- · Fully programmable timing

- Supports input pixel rates of 10 to 15 Mpps

- 256 x 8 x 3 color look-up tables (bypassable on TMC22191)

- · 8-bit mask register

- 8-bit composite digital video input

- Hardware and 24-bit data keying

- Synchronizes with TMC22071 Genlocking Video Digitizer

- 8:8:8 video reconstruction

- SMPTE 170M NTSC or CCIR Report 624 PAL compatible

- · Supports PAL-M and NTSC without pedestal

- Simultaneous S-VIDEO (Y/C) NTSC/PAL output

- 10-bit D/A conversion (three channels)

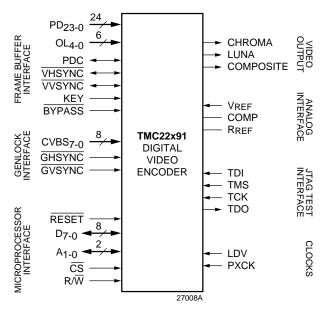

## Logic Symbol

BYPASS and OL4:0 on TMC22191 only.

- Controlled edge rates

- 3 power-down modes

- Built-in color bars and modulated ramp test signals

- JTAG (IEEE Std 1149.1-1990) test interface

- Single +5V power supply

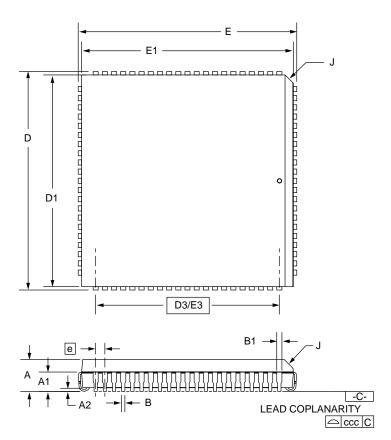

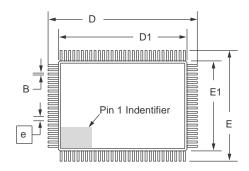

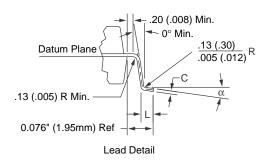

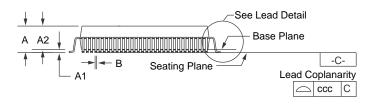

- 84 lead PLCC package

- 100 lead MQFP package

## **Description**

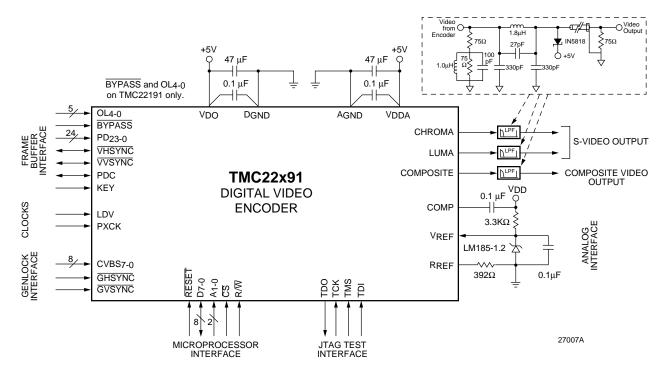

The TMC22x91 digital video encoders convert digital computer image or graphics data (in RGB, YCBCR, or color indexed format) or a CCIR-601 signal into a standard analog baseband television (NTSC or PAL) signal with a modulated color subcarrier.

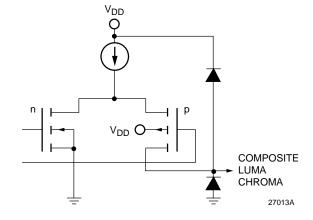

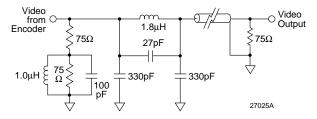

Both composite (single lead) and S-VIDEO (separate chroma and luma) formats are active simultaneously at the three analog output pins, each of which generates a standard video-level signal into doubly-terminated 75 $\Omega$  load.

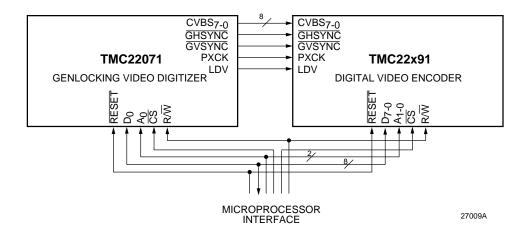

The TMC22x91 accepts digitized video from the companion TMC22071 Genlocking Video Digitizer. Soft switching between video sources is done under either hardware or programmable data control.

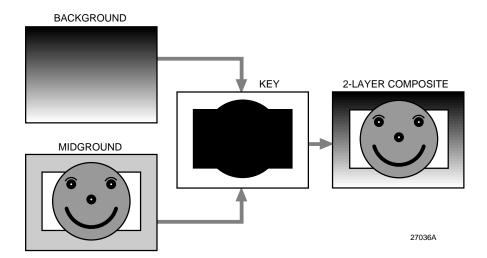

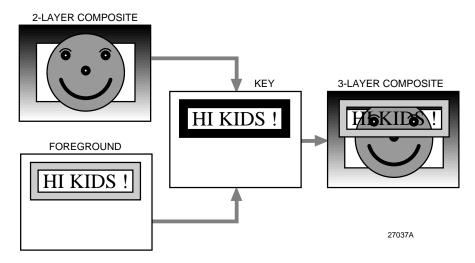

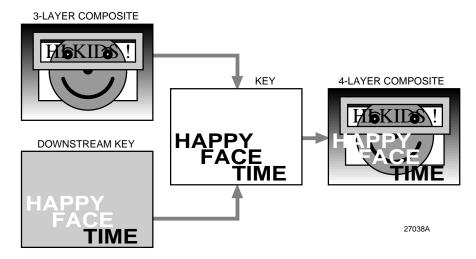

The TMC22191 offers 4-layer keying capability, bypassable CLUT, and 30 Overlay colors.

The TMC22x91 is fabricated in a submicron CMOS process and packaged in an 84 Lead Plastic Leadless Chip Carrier, or in a 100 Lead Metric Quad Flat Pack. Performance is guaranteed from 0°C to 70°C.

## **Block Diagram**

## **Functional Description**

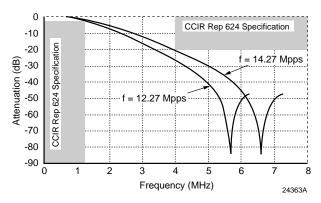

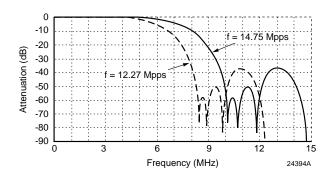

The TMC22091 and TMC22191 are totally integrated, fully-programmable digital video encoders with simultaneous composite and Y/C (S-VIDEO) outputs. The TMC22x91 video outputs are compatible with SMPTE 170M NTSC, CCIR Report 624 PAL, PAL-M, and NTSC without pedestal television standards. No external component selection or tuning is required.

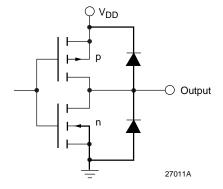

The encoders accept digital image data at the PD port in one of several formats, which are matrixed into luminance and chrominance components. The chrominance signals are modulated onto a digitally synthesized subcarrier. The luminance and chrominance signals are separately interpolated to twice the pixel rate, and converted to analog levels by 10-bit D/A converters. They are also digitally combined and the resulting composite signal is output by a third 10-bit D/A converter. This composite signal may be keyed (pixel rate switching) with a second composite digital video signal presented to the encoder.

The output video frames may be internally timed by the TMC22x91, synchronized with the external frame buffer, or slaved to the companion Genlocking Video Digitizer (TMC22071). All operational parameters are fully programmable over a standard microprocessor port.

Table 1 shows the key features that distinguish between the TMC22091 and TMC22191. All of the information presented in this data sheet applies to both products unless otherwise noted. Statements, paragraphs, tables, and figures that apply to only one or two of the encoders have notation specifying the applicable part number.

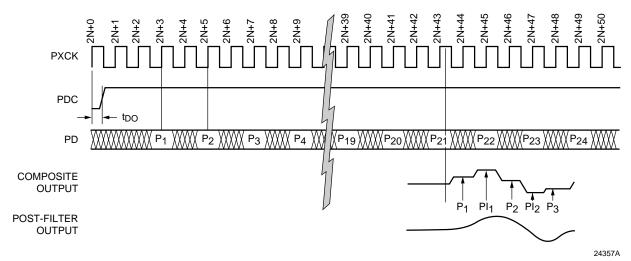

### **Timing**

The encoder operates from a single clock at twice the system pixel rate. This frequency may be set between 20 MHz and 36 MHz (pixel rates of 10 Mpps to 18 Mpps). Within this range are included CCIR-601, D2, and square-pixel formats, as well as a variety of computer-specific pixel rates. An array of programmable timing registers allows the software selection of all pertinent signal parameters to produce NTSC (with or without 7.5 IRE pedestal) and PAL, and PAL-M outputs.

Table 1. Comparing the TMC22x91 Encoders

| Feature                                              | TMC22091 | TMC22191 |

|------------------------------------------------------|----------|----------|

| OL <sub>4-0</sub> pixel inputs for 30 overlay colors | No       | Yes      |

| Number of video layers supported                     | 2        | 4        |

| BYPASS input for bypassing CLUTs                     | No       | Yes      |

### Input Formatting

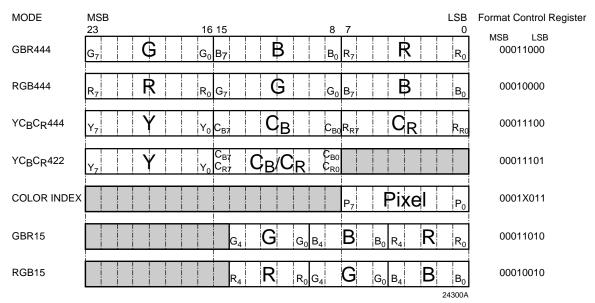

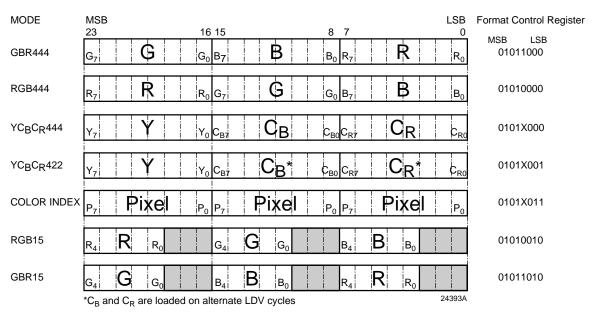

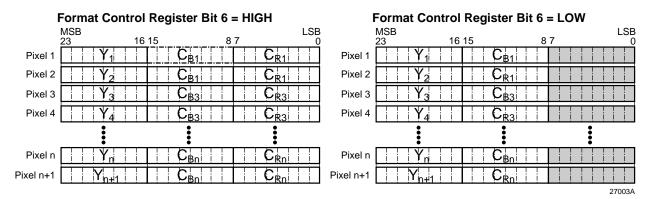

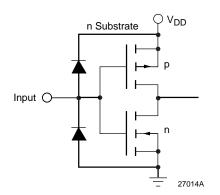

The input section accepts a variety of video and graphics formats, including 24-bit GBR and RGB, 15-bit GBR and RGB, YCBCR422, YCBCR444, and 8-bit color-indexed data (Figure 1a and 1b).

The input section of the TMC22x91 includes a key comparator which monitors the pixel data port with three independent 8-bit comparators, and invokes a video key when the selected registers match the incoming data.

### **Mask Register**

A Mask Register is provided which is logically ANDed with incoming color-index data to facilitate pixel animation and other special graphics effects. The Mask Register is ahead of the Data Key comparators and is enabled only when color-index input is selected. Mask Register programming and operation are similar to that of the 171/176 family of graphics RAMDACS.

### **Color Lookup Table**

The Color Lookup Table (CLUT) is a 256 x 8 x 3 random-access memory. It provides means for offset, gain, gamma, and color correction in RGB and YCBCR operating modes. It provides a full 24-bit color lookup function for color-index mode. It can be loaded in the same manner as a standard VGA RAMDAC.

# **Colorspace Conversion Matrix and Interpolator**

The matrix converts RGB data (whether from RGB inputs or color-indexed CLUT data) into Y, B-Y, R-Y format for encoding. In input configurations where the pixel input is already in Y, B-Y, R-Y format, the matrix is bypassed. When pixel data is input in YCBCR422 format, the interpolation filters produce YCBCR444 for encoding.

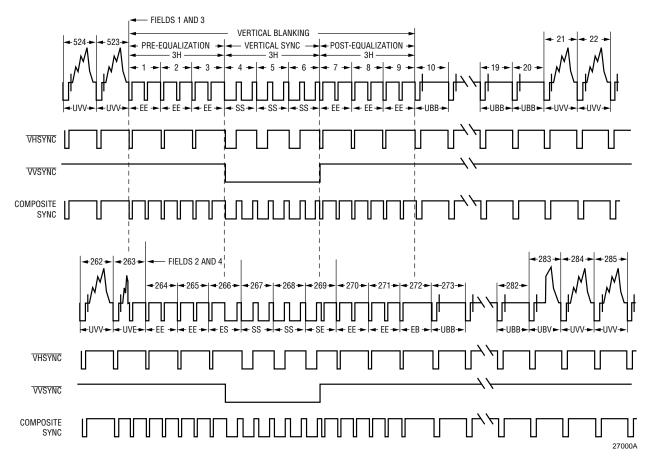

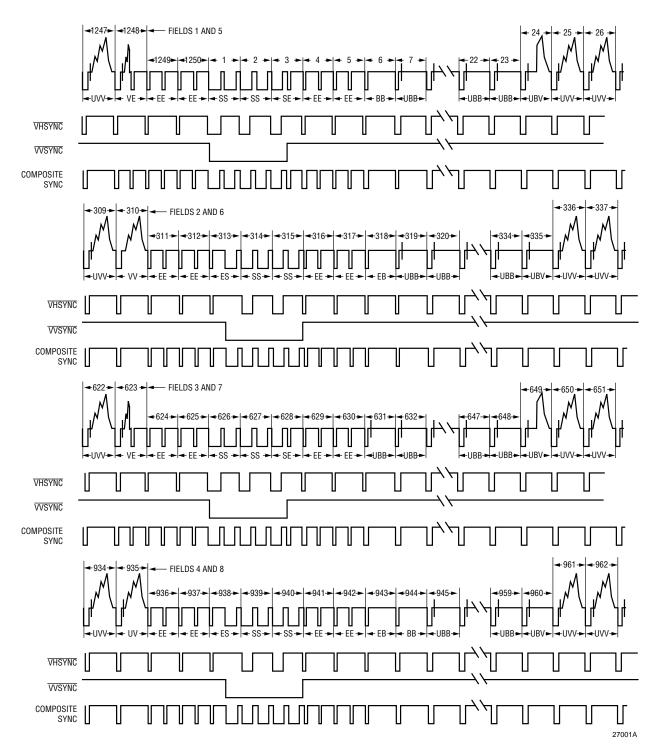

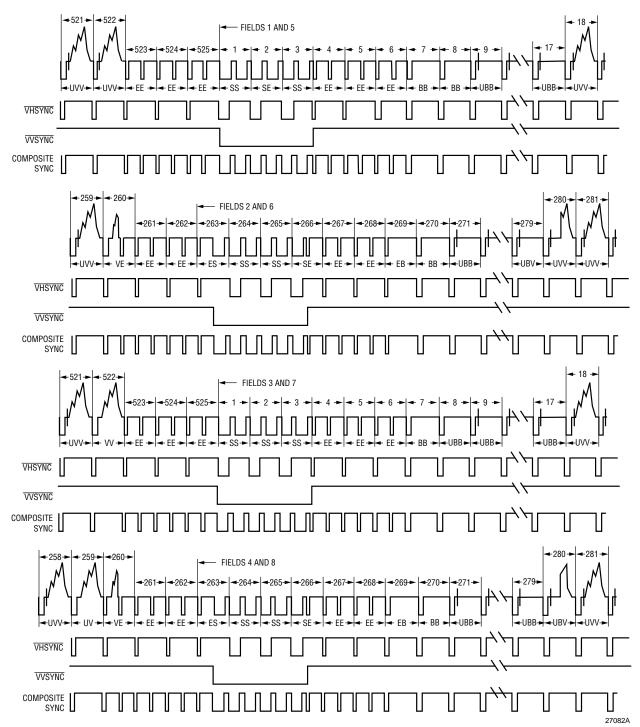

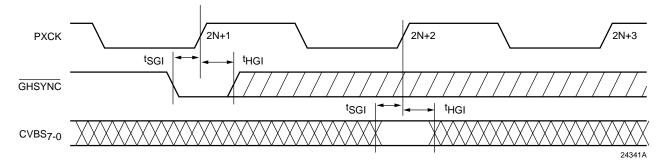

### **Sync Generator**

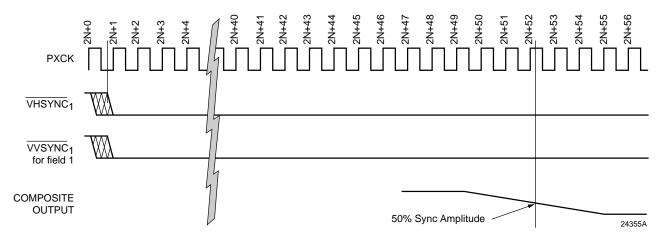

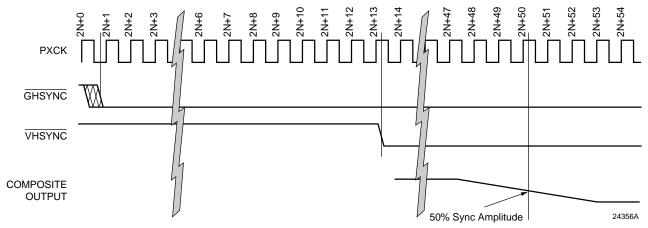

The TMC22x91 can operate in Master, Genlock, or Slave modes. In Master and Genlock modes, the encoder internally generates all timing and sync signals, and provides Horizontal Sync, Vertical Sync, and Pixel Data Control (PDC) to the external frame buffer circuitry. PDC is independently selectable to function as an input or an output. In Genlock mode, the TMC22x91 timing is controlled by the TMC22071 Genlocking Video Digitizer over the CVBS7-0 bus, GVSYNC, and GHSYNC. The encoder, in turn, produces VHSYNC, VVSYNC, and PDC for the frame buffer interface.

Figure 1a. Pixel Data Format

Figure 1b. Pixel Data Format (TMC22191 when CLUTs are Bypassed)

In Slave mode, VHSYNC, VVSYNC, and PDC (optional) are inputs to the TMC22x91. These inputs determine when new lines, frames, and active picture areas begin. The external controlling circuitry needs to establish the correct timing for these signals.

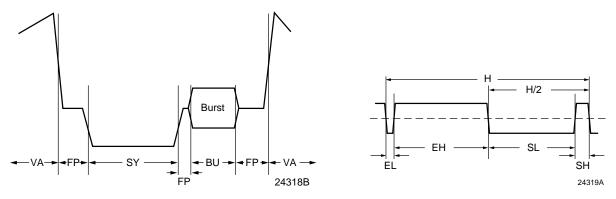

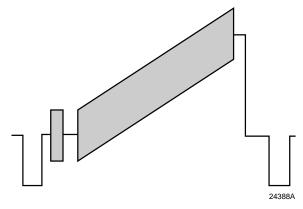

Horizontal and vertical synchronization signals are digitally generated by the TMC22x91 with controlled rise and fall times on all sync edges, the beginning and end of active video, and the burst envelope. All elements of horizontal sync timing are programmable, as are the frequency, phase, and duration of color burst.

### Video Input

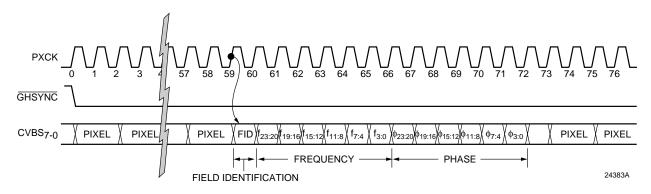

The TMC22x91 accepts genlocked synchronization data and digital composite video signals from the TMC22071 Genlocking Video Digitizer over the 8-bit CVBS bus. The encoder synchronizes its digital subcarrier oscillator to the video input from the TMC22071 with this data. The composite video data output from the TMC22071 is passed to the internal video switch for keying with the encoded pixel data.

### **Chroma Modulator**

A 32-bit digital subcarrier synthesizer feeds a quadrature modulator, producing a digital chrominance signal. The relative phases of the burst and active video portions of the subcarrier can be individually adjusted to compensate for external phase errors and to effect a hue control.

### **Interpolation Filters**

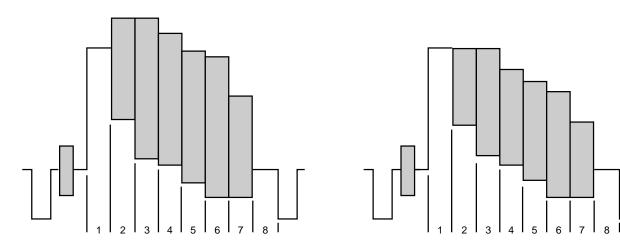

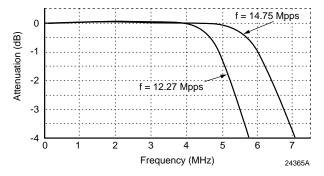

Interpolation filters on the luminance and chrominance signals double the pixel rate in preparation for D/A conversion. This band-limited process greatly simplifies the output filtering required following the D/A converters and dramatically reduces  $\sin(x)/x$  distortion.

An interpolation filter on the CVBS data similarly raises the sample rate of the video signal, for mixing with the encoded pixel data.

### **Composite Video Switch**

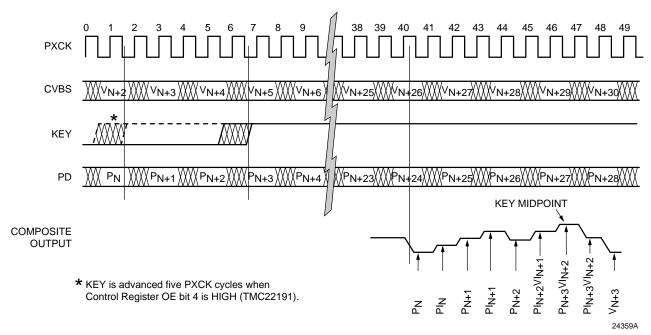

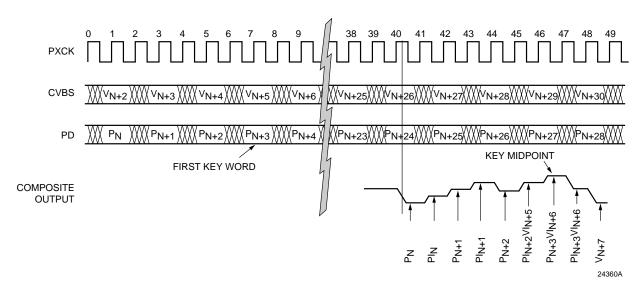

The Composite Video Switch selects between the composite video input (CVBS) and the composite encoded pixel data on a pixel-by-pixel basis, under the control of a key function.

Keying may be managed by hardware or software. The hardware key input (KEY pin) directly controls the video switch. The encoder may be programmed to operate with a data key, represented by three 8-bit registers that compare with the 24 input bits. They operate in all input modes and may be individually enabled or disabled.

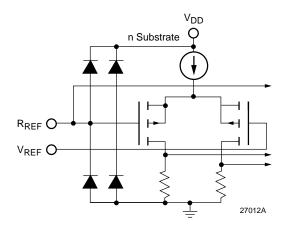

### **D/A Converters**

The analog outputs of the TMC22x91 are the outputs of three 10-bit D/A converters, operating at twice the pixel clock rate. The outputs are capable of driving standard video levels into a doubly-terminated  $75\Omega$  coaxial video cable (37.5 $\Omega$  total load). An internal voltage reference is provided which can be used to provide reference current for the three D/A converters. For accurate video levels, an external fixed or variable voltage reference source is recommended. The video signal levels from the TMC22x91 may be adjusted to overcome the insertion loss of analog low-pass output filters.

The D/A converters on the TMC22x91 may be powered-down via Control Register 0E bits 5 and 6. The COMPOSITE D/A is controlled by bit 6 and the LUMA and CHROMA D/A converters are controlled by bit 5.

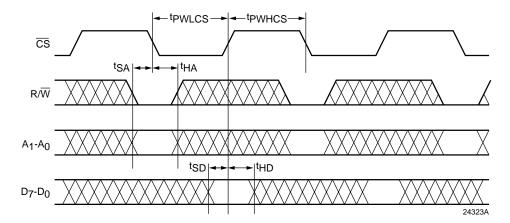

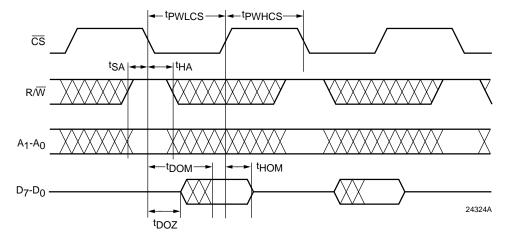

### **Microprocessor Interface**

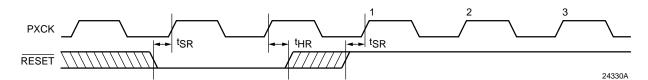

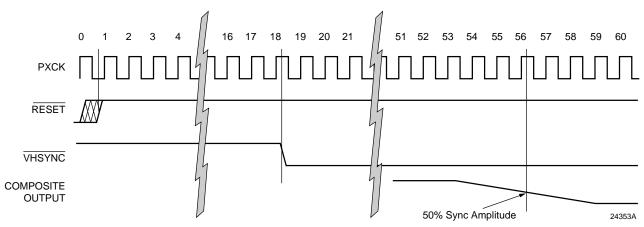

The microprocessor interface employs a 13 line format. The RESET pin sets all internal state machines to their initialized conditions, disables the analog outputs, sets the internal SRESET bit LOW (reset condition), and places the encoder in a power-down mode. All register and CLUT data are maintained in power-down mode. If the HRESET bit is set HIGH, line 1 field 1 is started when RESET goes HIGH, and SRESET is ignored. If HRESET is LOW, the encoder remains idle after RESET goes HIGH until Control Register bit SRESET is set HIGH, which initiates line 1 field 1.

Two address lines are provided and decoded for access to the internal Control Registers and CLUT. Control Registers and CLUT are accessed by loading a desired address through the 8-bit D<sub>7-0</sub> port, followed by the desired data read or write for that address. Both the CLUT and the Control Registers are self-indexing, allowing continuous reads or writes to successive addresses.

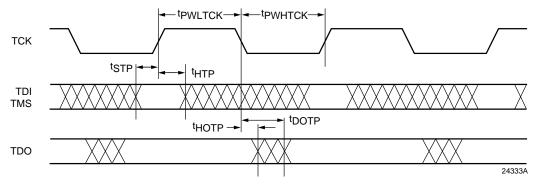

### **JTAG Test Interface**

The TMC22x91 includes a standard 4-line JTAG (IEEE Std 1149.1-1990) test interface port, providing access to all digital input/output data pins. This is provided to facilitate component and board-level testing.

### **Test/Validation Mode**

The TMC22x91 may be configured to produce standard color bars or a 40 IRE modulated (or unmodulated) video ramp, independent of any pixel or video data input. Color

bars are useful as an idle system output signal. The test signals may be used to verify proper operation of the analog video signal chain.

## TMC22090/TMC22190 Compatibility

The TMC22090 and TMC22190 are earlier versions of the TMC22091 and TMC22191, respectively. They lack the following features of the newer versions:

- 1. Selectable Setup (to support NTSC EIA-J video output for Japan)

- 2. PAL-M format (for South American applications)

- Extended EH and SL intervals (to support pixel rates above 15 Mpps)

- Individual D/A power-down (to reduce total dissipation when some outputs are not required)

- 5. Luminance I/O processing (to reduce flicker in graphics applications)

These features are controlled by registers 0E and 0F, and enabled by setting Register OE bit 7 to ONE. If an application of the TMC22x90 is programmed with this bit set to ZERO (as recommended in the product documentation) then the corresponding TMC22x91 will perform identically. Though the earlier parts continue to be available, it is recommended that the newer devices be used in new designs for the additional flexibility. Older designs may be readily converted to the newer versions to take advantage of the added features and lower cost of the later technology.

# **Pin Assignments**

## 84 Lead PLCC

| Pin | Name              | Pin | Name             | Pin | Name                   | Pin | Name              |

|-----|-------------------|-----|------------------|-----|------------------------|-----|-------------------|

| 1   | CVBS <sub>2</sub> | 22  | TD0              | 43  | VDDA                   | 64  | V <sub>DD</sub>   |

| 2   | CVBS <sub>1</sub> | 23  | TCK              | 44  | CVBS <sub>7</sub>      | 65  | D <sub>GND</sub>  |

| 3   | CVBS <sub>0</sub> | 24  | TMS              | 45  | CVBS <sub>6</sub>      | 66  | PD <sub>11</sub>  |

| 4   | KEY               | 25  | TDI              | 46  | CVBS <sub>5</sub>      | 67  | PD <sub>10</sub>  |

| 5   | RESET             | 26  | D <sub>GND</sub> | 47  | CVBS <sub>4</sub>      | 68  | PD <sub>9</sub>   |

| 6   | CS                | 27  | V <sub>DD</sub>  | 48  | OL <sub>3</sub> (TEST) | 69  | PD8               |

| 7   | R/W               | 28  | BYPASS (TEST)    | 49  | OL <sub>2</sub> (TEST) | 70  | PD <sub>7</sub>   |

| 8   | A <sub>1</sub>    | 29  | OL4 (TEST)       | 50  | OL <sub>1</sub> (TEST) | 71  | PD <sub>6</sub>   |

| 9   | A <sub>0</sub>    | 30  | V <sub>REF</sub> | 51  | OL <sub>0</sub> (TEST) | 72  | PD <sub>5</sub>   |

| 10  | DGND              | 31  | R <sub>REF</sub> | 52  | PD <sub>23</sub>       | 73  | PD <sub>4</sub>   |

| 11  | PDC               | 32  | AGND             | 53  | PD <sub>22</sub>       | 74  | PD <sub>3</sub>   |

| 12  | VHSYNC            | 33  | COMPOSITE        | 54  | PD <sub>21</sub>       | 75  | PD <sub>2</sub>   |

| 13  | VVSYNC            | 34  | AGND             | 55  | PD <sub>20</sub>       | 76  | PD <sub>1</sub>   |

| 14  | D <sub>7</sub>    | 35  | LUMA             | 56  | PD <sub>19</sub>       | 77  | PD <sub>0</sub>   |

| 15  | D <sub>6</sub>    | 36  | AGND             | 57  | PD <sub>18</sub>       | 78  | LDV               |

| 16  | D <sub>5</sub>    | 37  | CHROMA           | 58  | PD <sub>17</sub>       | 79  | PXCK              |

| 17  | D <sub>4</sub>    | 38  | AGND             | 59  | PD <sub>16</sub>       | 80  | DGND              |

| 18  | D <sub>3</sub>    | 39  | COMP             | 60  | PD <sub>15</sub>       | 81  | $V_{DD}$          |

| 19  | D <sub>2</sub>    | 40  | $V_{DDA}$        | 61  | PD <sub>14</sub>       | 82  | GVSYNC            |

| 20  | D <sub>1</sub>    | 41  | V <sub>DDA</sub> | 62  | PD <sub>13</sub>       | 83  | GHSYNC            |

| 21  | D <sub>0</sub>    | 42  | VDDA             | 63  | PD <sub>12</sub>       | 84  | CVBS <sub>3</sub> |

Note: Pin names in parentheses apply to TMC22091.

### 100 Lead MQFP

| Pin | Name                   | Pin | Name             | Pin | Name              | Pin | Name                   |

|-----|------------------------|-----|------------------|-----|-------------------|-----|------------------------|

| 1   | NC                     | 26  | PD <sub>23</sub> | 51  | PD3               | 76  | DGND                   |

| 2   | COMPOSITE              | 27  | PD <sub>22</sub> | 52  | NC                | 77  | PDC                    |

| 3   | NC                     | 28  | NC               | 53  | NC                | 78  | NC                     |

| 4   | AGND                   | 29  | NC               | 54  | NC                | 79  | NC                     |

| 5   | LUMA                   | 30  | NC               | 55  | NC                | 80  | VHSYNC                 |

| 6   | AGND                   | 31  | PD <sub>21</sub> | 56  | PD <sub>2</sub>   | 81  | VVSYNC                 |

| 7   | NC                     | 32  | PD <sub>20</sub> | 57  | PD <sub>1</sub>   | 82  | D <sub>7</sub>         |

| 8   | CHROMA                 | 33  | PD <sub>19</sub> | 58  | PD <sub>0</sub>   | 83  | D <sub>6</sub>         |

| 9   | AGND                   | 34  | PD <sub>18</sub> | 59  | LDV               | 84  | D <sub>5</sub>         |

| 10  | COMP                   | 35  | PD <sub>17</sub> | 60  | PXCK              | 85  | D4                     |

| 11  | NC                     | 36  | PD <sub>16</sub> | 61  | DGND              | 86  | D <sub>3</sub>         |

| 12  | NC                     | 37  | PD <sub>15</sub> | 62  | $V_{DD}$          | 87  | D <sub>2</sub>         |

| 13  | $V_{DDA}$              | 38  | PD <sub>14</sub> | 63  | GVSYNC            | 88  | D <sub>1</sub>         |

| 14  | $V_{DDA}$              | 39  | PD <sub>13</sub> | 64  | GHSYNC            | 89  | D <sub>0</sub>         |

| 15  | $V_{DDA}$              | 40  | PD <sub>12</sub> | 65  | CVBS <sub>3</sub> | 90  | TD0                    |

| 16  | VDDA                   | 41  | VDD              | 66  | CVBS <sub>2</sub> | 91  | TCK                    |

| 17  | VDDA                   | 42  | DGND             | 67  | CVBS <sub>1</sub> | 92  | TMS                    |

| 18  | CVBS <sub>7</sub>      | 43  | PD <sub>11</sub> | 68  | CVBS <sub>0</sub> | 93  | TDI                    |

| 19  | CVBS <sub>6</sub>      | 44  | PD <sub>10</sub> | 69  | NC                | 94  | D <sub>GND</sub>       |

| 20  | CVBS <sub>5</sub>      | 45  | PD <sub>9</sub>  | 70  | KEY               | 95  | V <sub>DD</sub>        |

| 21  | CVBS <sub>4</sub>      | 46  | PD <sub>8</sub>  | 71  | RESET             | 96  | BYPASS (TEST)          |

| 22  | OL <sub>3</sub> (TEST) | 47  | PD <sub>7</sub>  | 72  | CS                | 97  | OL <sub>4</sub> (TEST) |

| 23  | OL <sub>2</sub> (TEST) | 48  | PD <sub>6</sub>  | 73  | R/W               | 98  | VREF                   |

| 24  | OL <sub>1</sub> (TEST) | 49  | PD <sub>5</sub>  | 74  | A <sub>1</sub>    | 99  | RREF                   |

| 25  | OL <sub>0</sub> (TEST) | 50  | PD4              | 75  | A <sub>0</sub>    | 100 | AGND                   |

Note: Pin names in parentheses apply to TMC22091.

# **Pin Descriptions**

|                        | Pin N           | umber                                |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|------------------------|-----------------|--------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name               | 84-Lead<br>PLCC | 100-Lead<br>MQFP                     | Value | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Clocks                 |                 |                                      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

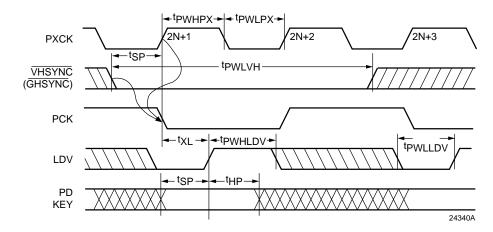

| PXCK                   | 79              | 60                                   | TTL   | Master Clock Input. This 20 to 30 MHz clock is internally divided by 2 to generate the internal pixel clock, PCK, which a LOW on RESET forces LOW. PXCK drives the entire TMC22x91, except the asynchronous microprocessor interface and the semi-synchronous LDV data input clock. All internal registers are strobed on the rising edge of PXCK.                                                                                                                                                                                                                                                        |  |  |

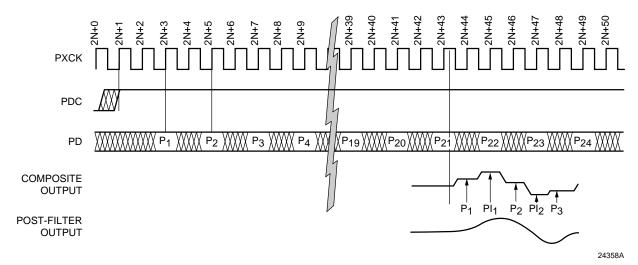

| LDV                    | 78              | 59                                   | TTL   | <b>Pixel Data Load Clock.</b> On each rising edge of LDV, data on PD <sub>23-0</sub> are latched into the input preload register, for transfer into the input demultiplexer on the next rising edge of PCK.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Frame Buffer Interface |                 |                                      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| PD23-0                 | 52-63,<br>66-77 | 26, 27,<br>31-40,<br>43-51,<br>56-58 | TTL   | <b>Pixel Data Inputs.</b> In YCBCR, GBR, RGB, and color-indexed mode, pixel data enter the TMC22x91 on PD <sub>23-0</sub> . The specific format is found in Figures 1a and 1b. LDV is the clock that controls the loading of pixel data.                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| VHSYNC                 | 12              | 80                                   | TTL   | Horizontal Sync I/O. In Master and Genlock modes, the TMC22x91 outputs horizontal sync on this pin. In Slave modes, the TMC22x91 accepts and locks to horizontal sync input on this pin (with vertical sync on \(\frac{VVSYNC}{VSYNC}\)). \(\frac{VHSYNC}{VHSYNC}\) and \(\frac{VVSYNC}{VVSYNC}\) on the same rising edge of PXCK.                                                                                                                                                                                                                                                                        |  |  |

| VVSYNC                 | 13              | 81                                   | TTL   | Vertical Sync I/O. In separate V and H sync Master and Genlock modes, the TMC22x91 outputs vertical block sync (VVSYNC LOW for the 2.5 (PAL) or 3 (NTSC) lines on which vertical sync pulses occur). In composite sync (H and V sync on same signal) Master and Genlock modes, the TMC22x91 outputs horizontal sync, vertical sync, and equalization over this pin. In Slave mode, the TMC22x91 accepts and locks to vertical sync input on this pin (with horizontal sync on VHSYNC). VHSYNC and VVSYNC must be coincident such that they are clocked into the TMC22x91 on the same rising edge of PXCK. |  |  |

| PDC                    | 11              | 77                                   | TTL   | <b>Pixel Data Control.</b> In Master mode, the TMC22x91 forces PDC HIGH when and only when it wants active video from the frame buffer. During blanking (syncs, equalization, burst, and porches), it forces PDC LOW, signaling that it will ignore any data presented over PD <sub>23-0</sub> . When PDC is used as an input, forcing it HIGH allows the TMC22x91 to receive PD during the active video state.                                                                                                                                                                                           |  |  |

| KEY                    | 4               | 70                                   | TTL   | Hardware Key Input. When the HKEN control bit is set HIGH and hardware key pin, KEY, is HIGH, video data entering on CVBS7-0 are routed to the COMPOSITE output. This control signal is pipelined so the pixel that is presented to the PD port when the KEY signal is invoked is at the midpoint of the soft key transition. When HKEN is LOW, KEY is ignored. Like PD data, KEY is clocked into the TMC22x91 on the rising edge of LDV.                                                                                                                                                                 |  |  |

# Pin Descriptions (continued)

|                     | Pin N             | umber            |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|---------------------|-------------------|------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name            | 84-Lead<br>PLCC   | 100-Lead<br>MQFP | Value | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| OL4-0               | 29, 48-51         | 97, 22-25        | TTL   | Overlay Data Inputs (TMC22191 only). 30 of the 256 locations of the CLUT may be reserved for overlay operation. These CLUT locations are directly accessed by five input pins, OL4-0. OL4-0 are entered into the TMC22191 on a pixel-by-pixel basis and select which of the 30 overlay colors is to be encoded. When all five OL4-0 inputs are LOW, no overlay occurs.                                                                                                                                                                                                                                                                               |  |  |

| BYPASS              | 28                | 96               | TTL   | CLUT Bypass Control (TMC22191 only). When BYPASS is HIGH, the CLUT is in the pixel data path within the TMC22191. When BYPASS is LOW, pixel data bypasses the CLUT. BYPASS is active only for certain modes of the Layering Control Register (LCR) when the Format Control Register bit 6 is HIGH.                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Genlock Interface   |                   |                  |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| GHSYNC              | 83                | 64               | CMOS  | Genlock Horizontal Sync. In Genlock mode, the TMC22x91 will start a new horizontal line (blank-to-sync-edge transition) with each falling edge of GHSYNC. In non-genlock modes, the TMC22x91 ignores GHSYNC. The internal pixel clock, PCK, is aligned with the falling edge of VHSYNC or GHSYNC (Genlock mode).                                                                                                                                                                                                                                                                                                                                     |  |  |

| GVSYNC              | 82                | 63               | CMOS  | Genlock Vertical Sync. In Genlock mode, the TMC22x91 will start a new vertical sync sequence at line 1 field 1 whenever GVSYNC and GHSYNC are coincident such that they are clocked into the TMC22x91 on the same rising edge of PXCK. If GVSYNC falls at any other time, the TMC22x91 will assume that this marks the start of field 2, and will ignore it (in odd-field sync mode) or (in all-field sync mode) respond by generating a single vertical sync pulse, followed by 2 (PAL) or 2.5 (NTSC) lines of vertical sync, keyed to the next falling edge on GHSYNC. See Interface Control Register bit 0 for odd-field and all-field operation. |  |  |

| CVBS <sub>7-0</sub> | 44-47, 84,<br>1-3 | 18-21,<br>65-68  | TTL   | Composite Video Inputs. The encoder receives digitized video, subcarrier phase, and subcarrier frequency over this 8-bit bus at the PCK rate. This data may be provided by the companion TMC22071 Genlocking Video Digitizer. In Genlock mode, the TMC22x91 expects subcarrier phase and frequency data during each line's horizontal sync interval, as well as video data when keying is engaged, transferred at the PCK rate.                                                                                                                                                                                                                      |  |  |

| Microprocess        | or Interface      | )                |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| D <sub>7-0</sub>    | 14-21             | 82-89            | TTL   | Data I/O Port. All control parameters are loaded into and read back over this 8-bit port. For digital testing, the five lower bits can also serve as a two-cycle 10-bit data output port. For D/A converter testing, it can be used as a 10-bit two-cycle input port, facilitating, for example, ramp-based D/A converter linearity tests.                                                                                                                                                                                                                                                                                                           |  |  |

| A <sub>1-0</sub>    | 8-9               | 74-75            | TTL   | µProc Port Controls. As in a RAMDAC, this control governs whether the microprocessor interface selects a table address or reads/writes table contents. It also governs setting and verification of the TMC22x91's internal operating modes, also over port D7-0.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

# Pin Descriptions (continued)

|                 | Pin N             | umber             |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|-------------------|-------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | 84-Lead           | 100-Lead          |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Pin Name        | PLCC              | MQFP              | Value              | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

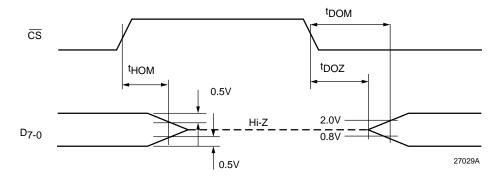

| CS              | 6                 | 72                | TTL                | Chip Select. When $\overline{CS}$ is HIGH, the microprocessor interface port, D <sub>7-0</sub> , is set to HIGH impedance and ignored. When $\overline{CS}$ is LOW, the microprocessor can read or write parameters over D <sub>7-0</sub> . One additional falling edge of $\overline{CS}$ is needed to move input data to its assigned working registers.                                                                                                                                                                                  |

| R/W             | 7                 | 73                | TTL                | <b>Bus Read/Write Control.</b> When $R/\overline{W}$ and $\overline{CS}$ are LOW, the microprocessor can write to the control registers or CLUT over D <sub>7-0</sub> . When $R/\overline{W}$ is HIGH and $\overline{CS}$ is LOW, it can read the contents of any CLUT address or control register over D <sub>7-0</sub> .                                                                                                                                                                                                                  |

| RESET           | 5                 | 71                | TTL                | Master Reset Input. Bringing RESET LOW sets the software reset control bit, SRESET, LOW, forcing the internal state machines to their starting states and disabling all outputs. Bringing RESET HIGH synchronizes the internal pixel clock (PCK = PXCK / 2) to maintain a defined pipeline delay through the TMC22x91. If HRESET is set HIGH, the encoder is enabled when RESET goes HIGH. If HRESET is LOW, the host restarts the TMC22x91 by setting SRESET HIGH. RESET does not affect the CLUT or the control registers, except SRESET. |

| Video Output    | -                 |                   |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| COMPOSITE       | 33                | 2                 | 1 V <sub>P-P</sub> | <b>NTSC/PAL Video.</b> Analog output of composite D/A converter, nominally 1.35 volt peak-to-peak into a 37.5Ω load.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LUMA            | 35                | 5                 | 1 V P-P            | <b>Luminance-only Video.</b> Analog output of luminance D/A converter, nominally 1.35 volt peak-to-peak into a 37.5Ω load.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CHROMA          | 37                | 8                 | 1 V P-P            | Chrominance-only Video. Analog output of chrominance D/A converter, nominally 1.35 volt peak-to-peak into a $37.5\Omega$ load.                                                                                                                                                                                                                                                                                                                                                                                                              |

| Analog Interfa  | ace               |                   |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VREF            | 30                | 98                | +1.23 V            | Voltage Reference Input. External voltage reference input, internal voltage reference output, nominally 1.235 V.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| COMP            | 39                | 10                | 0.1 μF             | Compensation Capacitor. Connection point for 0.1μf decoupling capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RREF            | 31                | 99                | 392Ω               | Current-setting Resistor. Connection point for external current-setting resistor for D/A converters. The resistor (392 $\Omega$ ) is connected between R <sub>REF</sub> and A <sub>GND</sub> . Output video levels are inversely proportional to the value of R <sub>REF</sub> .                                                                                                                                                                                                                                                            |

| JTAG Test Inte  | erface            |                   |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TDI             | 25                | 93                | TTL                | Data Input Port. Boundary scan data input port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TMS             | 24                | 92                | TTL                | Scan Select Input. Boundary scan (HIGH)/normal operation (LOW) selector.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TCK             | 23                | 91                | TTL                | Scan Clock Input. Boundary scan clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TDO             | 22                | 90                | TTL                | Data Output Port. Boundary scan data output port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Power Supply    |                   |                   |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>DD</sub> | 27, 64, 81        | 41, 62, 95        | +5 V               | Positive digital power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VDDA            | 40-43             | 13-17             | +5 V               | Positive analog power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DGND            | 10, 26, 65,<br>80 | 42, 61, 76,<br>94 | 0.0 V              | Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AGND            | 32, 34, 36,<br>38 | 4, 6, 9,<br>100   | 0.0 V              | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## Pin Descriptions (continued)

|          | Pin N            | umber                                               |       |                                                                                                                                                                                                                                              |

|----------|------------------|-----------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | 84-Lead<br>PLCC  | 100-Lead<br>MQFP                                    | Value | Pin Function Description                                                                                                                                                                                                                     |

| Test     |                  |                                                     |       |                                                                                                                                                                                                                                              |

| TEST     | 28, 29,<br>48-51 | 22-25,<br>96-97                                     | 0.0 V | Factory testing (TMC22091 only). Reserved for factory testing. These pins have no effect on the operation but do function as JTAG registers. They should be grounded directly or pulled down to ground with $1k\Omega$ or smaller resistors. |

| NC       | N/A              | 1, 3, 7,<br>11-12,<br>28-30,<br>52-55,<br>69, 78-79 |       | No Connect                                                                                                                                                                                                                                   |

## **Control Registers**

The TMC22x91 is initialized and controlled by a set of registers. The registers are organized into 13 categories:

- 1. Global Control

- 2. Format Control

- 3. Interface Control

- 4. Test Control

- 5. Key Control

- 6. Misc. Control

- Standards Control

- 8. Layering Control (TMC22191)

- 9. Key Value

- 10. Timing

- 11. Subcarrier

- 12. Test I/O

- 13. Mask Register

An external controller loads the Control Registers through a standard interface port. It also loads the CLUT and reads its

contents or those of the Control Registers. The port is governed by pins  $\overline{CS}$ ,  $R/\overline{W}$ , and  $A_{1-0}$ .

The Address Register for the CLUT and the Control Register pointer automatically increment to allow successive writes to sequential addresses. In the CLUT, the Address Register has two additional bits which increment in modulo-three to sequentially access the red, green, and blue portions. All three colors must be written when any CLUT address is changed.

The control register autoincrement follows the sequence indicated in the Control Register Map. When it reaches address 40, it stops incrementing, allowing multiple reads or writes of test data from/to the TESTDAT register. To exit the test mode, reset the Control Register pointer by setting A1-0, D7-0, and  $R/\overline{W}$  LOW and then bring  $\overline{CS}$  LOW. Address 1F is a read-only status register. It is addressed by the autoincrement sequencer. Any data may be written into this port at that time but it will not be stored. When address 50 is accessed, no autoincrement takes place, allowing multiple writes to the Mask Register.

**Table 2. Microprocessor Port Control**

| A1-0 | R/W | Action                                                 |

|------|-----|--------------------------------------------------------|

| 00   | 0   | Write D7-0 into Control Register pointer               |

| 00   | 1   | Read Control Register pointer on D <sub>7-0</sub>      |

| 01   | 0   | Write D <sub>7-0</sub> into CLUT Address Pointer       |

| 01   | 1   | Read CLUT Address Pointer on D7-0                      |

| 10   | 0   | Write D7-0 to addressed Control Register               |

| 10   | 1   | Read addressed Control<br>Register on D <sub>7-0</sub> |

| 11   | 0   | Write D <sub>7-0</sub> to addressed CLUT location      |

| 11   | 1   | Read addressed CLUT location on D <sub>7-0</sub>       |

**Table 3. Control Register Map**

| Reg    | Bit                        | Name           | Function                                          |  |  |  |  |

|--------|----------------------------|----------------|---------------------------------------------------|--|--|--|--|

| Globa  | Global Control Register    |                |                                                   |  |  |  |  |

| 00     | 7-5                        |                | Reserved                                          |  |  |  |  |

| 00     | 4                          | SRESET         | Software reset                                    |  |  |  |  |

| 00     | 3                          | PAL            | Standard select, NTSC or PAL                      |  |  |  |  |

| 00     | 2                          | LUMDIS         | Luminance input disable                           |  |  |  |  |

| 00     | 1                          | CHRDIS         | Chrominance input disable                         |  |  |  |  |

| 00     | 0                          | HRESET         | Software reset disable                            |  |  |  |  |

| Form   | at Coı                     | ntrol Register |                                                   |  |  |  |  |

| 01     | 7                          |                | Reserved                                          |  |  |  |  |

| 01     | 6                          | LCREN          | Layering Control<br>Register enable<br>(TMC22191) |  |  |  |  |

| 01     | 5                          | RAMPEN         | Modulated ramp test                               |  |  |  |  |

| 01     | 4                          | CB             | Color bar test                                    |  |  |  |  |

| 01     | 3-2                        | FORMAT         | PD <sub>23-0</sub> input format select            |  |  |  |  |

| 01     | 1-0                        | INMODE         | PD <sub>23-0</sub> input mode select              |  |  |  |  |

| Interf | Interface Control Register |                |                                                   |  |  |  |  |

| 02     | 7                          | VITSEN         | VITS lines enable                                 |  |  |  |  |

| 02     | 6                          | SHCY           | Short-cycle test mode                             |  |  |  |  |

| 02     | 5-4                        | TBASE          | Time-base source select                           |  |  |  |  |

| 02     | 3                          | SOUT           | Sync output mode select                           |  |  |  |  |

Table 3. Control Register Map (continued)

| Reg    | Bit    | Name           | Function                                 |

|--------|--------|----------------|------------------------------------------|

|        |        |                |                                          |

| 02     | 2      | FBDIS          | Frame buffer signals disable             |

| 02     | 1      | PDCDIR         | PDC master, slave select                 |

| 02     | 0      | FLDLK          | Field lock select                        |

| Test ( | Contro | ol Register    |                                          |

| 03     | 7      |                | Reserved                                 |

| 03     | 6      | LIMEN          | Luminance limiter enable                 |

| 03     | 5      | TESTEN         | Test enable                              |

| 03     | 4      | HOLDEN         | MSBs/LSBs hold select                    |

| 03     | 3      | TSTMSB         | LSBs, MSBs in/out select                 |

| 03     | 2      | LUMTST         | LUMA channel test                        |

| 03     | 1      | 8FSUBR         | 8-field subcarrier reset enable          |

| 03     | 0      | CHRTST         | CHROMA channel test                      |

| Key C  | ontro  | l Register     |                                          |

| 04     | 7      |                | Reserved                                 |

| 04     | 6      | HKEN           | Hardware key enable                      |

| 04     | 5      | BUKEN          | Burst key enable                         |

| 04     | 4      | SKEXT          | Data key operation select                |

| 04     | 3      | DKDIS          | Green/red/Y data key disable             |

| 04     | 2      | EKDIS          | Blue/green/CB data key disable           |

| 04     | 1      | FKDIS          | Red/blue/C <sub>R</sub> data key disable |

| 04     | 0      | SKEN           | Data key enable                          |

| Layer  | ing C  | ontrol Registe | er (TMC22191)                            |

| 04     | 7      | LAYMODE        | MSB of Layer<br>Assignments select       |

| 04     | 6      | HKEN           | Hardware key enable                      |

| 04     | 5      | BUKEN          | Burst key enable                         |

| 04     | 4      | SKEXT          | Data key operation select                |

| 04     | 3-1    | LAYMODE        | LSBs of Layer<br>Assignments select      |

| 04     | 0      | SKEN           | Data key enable                          |

| Key V  | alue I | Registers      |                                          |

| 05     | 7-0    | DKEY           | Green/red/Y data key value               |

| 06     | 7-0    | EKEY           | Blue/green/CB data key value             |

Table 3. Control Register Map (continued)

| Reg                    | Bit   | Name          | Function                               |  |  |  |  |

|------------------------|-------|---------------|----------------------------------------|--|--|--|--|

| 07                     | 7-0   | FKEY          | Red/blue/C <sub>R</sub> data key value |  |  |  |  |

| 08-0D                  |       |               | Reserved                               |  |  |  |  |

| Misc. Control Register |       |               |                                        |  |  |  |  |

| 0E                     | 7     | EFEN          | Register 0E and 0F enable              |  |  |  |  |

| 0E                     | 6     | COMPD/A       | COMPOSITE D/A disable                  |  |  |  |  |

| 0E                     | 5     | SVIDD/A       | LUMA/CHROMA D/A disable                |  |  |  |  |

| 0E                     | 4     | FKREN         | Luminance processing enabled           |  |  |  |  |

| 0E                     | 3     | RATIO         | Luminance ratio select                 |  |  |  |  |

| 0E                     | 2     | TFLK          | Luminance pass threshold select        |  |  |  |  |

| 0E                     | 1     | T512          | EH/SL offset select                    |  |  |  |  |

| 0E                     | 0     | CB100         | NTSC/PAL Color Bars                    |  |  |  |  |

| Stand                  | lards | Control Regis | ster                                   |  |  |  |  |

| 0F                     | 7     | EFEN          | Same as Reg 0E bit 7<br>but read-only  |  |  |  |  |

| 0F                     | 6     | SIX25         | 625/525 line per frame select          |  |  |  |  |

| 0F                     | 5     | PALID         | Phase alternate line select            |  |  |  |  |

| 0F                     | 4     | SETUP         | 7.5 IRE Pedestal Enable                |  |  |  |  |

| 0F                     | 3-2   | YGAIN         | Luminance gain settings                |  |  |  |  |

| 0F                     | 1-0   | CGAIN         | Chrominance gain settings              |  |  |  |  |

| Timin                  | g Reg | jisters       |                                        |  |  |  |  |

| 10                     | 7-0   | SY            | Horizontal sync tip length             |  |  |  |  |

| 11                     | 7-0   | BR            | Breezeway length                       |  |  |  |  |

| 12                     | 7-0   | BU            | Burst length                           |  |  |  |  |

| 13                     | 7-0   | CBP           | Color back porch length                |  |  |  |  |

| 14                     | 7-0   | XBP           | Extended color back porch 8 LSB        |  |  |  |  |

| 15                     | 7-0   | VA            | Active video 8 LSB                     |  |  |  |  |

| 16                     | 7-0   | VC            | Active video start 8 LSB               |  |  |  |  |

| 17                     | 7-0   | VB            | Active video end 8 LSB                 |  |  |  |  |

| 18                     | 7-6   | XBP           | Extended color back porch 2 MSB        |  |  |  |  |

| 18                     | 5-4   | VA            | Active video 2 MSB                     |  |  |  |  |

| 18                     | 3-2   | VC            | Active video start 2 MSB               |  |  |  |  |

| 18                     | 1-0   | VB            | Active video end 2 MSB                 |  |  |  |  |

Table 3. Control Register Map (continued)

| Reg    | Bit               | Name         | Function                             |  |  |  |  |

|--------|-------------------|--------------|--------------------------------------|--|--|--|--|

| 19     | 7-0               | FP           | Front porch length                   |  |  |  |  |

| 1A     | 7-0               | EL           | Equalization pulse LOW length        |  |  |  |  |

| 1B     | 7-0               | EH           | Equalization pulse HIGH length       |  |  |  |  |

| 1C     | 7-0               | SL           | Vertical sync LOW length             |  |  |  |  |

| 1D     | 7-0               | SH           | Vertical sync HIGH length            |  |  |  |  |

| 1E     | 7-0               | CBL          | Color bar length                     |  |  |  |  |

| 1F     | 7-5               | FIELD        | Field identification                 |  |  |  |  |

| 1F     | 4-0               | LTYPE        | Line type identification             |  |  |  |  |

| Subc   | arrier            | Registers    |                                      |  |  |  |  |

| 20     | 7-0               | FREQL        | Subcarrier frequency 4th byte (LSBs) |  |  |  |  |

| 21     | 7-0               | FREQ3        | Subcarrier frequency 3rd byte        |  |  |  |  |

| 22     | 7-0               | FREQ2        | Subcarrier frequency<br>2nd byte     |  |  |  |  |

| 23     | 7-0               | FREQM        | Subcarrier frequency 1st byte (MSBs) |  |  |  |  |

| 24     | 7-0               | SYSPHL       | Video phase offset LSBs              |  |  |  |  |

| 25     | 7-0               | SYSPHM       | Video phase offset<br>MSBs           |  |  |  |  |

| 26     | 7-0               | BURPHL       | Burst phase offset LSBs              |  |  |  |  |

| 27     | 7-0               | BURPHM       | Burst phase offset MSBs              |  |  |  |  |

| 28-3F  |                   |              | Reserved                             |  |  |  |  |

| Test I | Test I/O Register |              |                                      |  |  |  |  |

| 40     | 7-0               | TESTDAT      | Test data input/output               |  |  |  |  |

| Mask   | Regis             | ster         |                                      |  |  |  |  |

| 50     | 7-0               | MASK         | Mask register                        |  |  |  |  |

| Y-Co   | mpon              | ent Register |                                      |  |  |  |  |

| 60     | 7-0               | Υ            | Y-component input/<br>output         |  |  |  |  |

### Notes:

- Functions are listed in the order used for reading and writing.

- For each register listed above, all bits not listed are reserved and should be set to zero to ensure proper operation.

- The meaning of Register 04 (Key Control Register/Layering Control Register) is determined by Format Control Register bit 6 (TMC22191).

# **Control Register Definitions**

# Global Control Register (00)

| 7 | 6        | 5        | 4 | 3 | 2      | 1      | 0      |

|---|----------|----------|---|---|--------|--------|--------|

|   | Reserved | Reserved |   |   | LUMDIS | CHRDIS | HRESET |

| Reg | Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00  | 7-5 |        | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 00  | 4   | SRESET | Software reset. When LOW, resets and holds internal state machines and disables outputs. When HIGH (normal), starts and runs state machines and enables outputs.                                                                                                                                                                                                                                                                                                                                                                            |

| 00  | 3   | PAL    | Video standard select. When LOW, the NTSC standard is generated with 7.5 IRE pedestal. When HIGH, PAL standard video is generated. This bit is ignored if Register 0E bit 7 is HIGH, enabling the 0E and 0F registers.                                                                                                                                                                                                                                                                                                                      |

| 00  | 2   | LUMDIS | Luminance input disable. When LOW (normal), luminance (Y) data from external frame buffer is enabled. When HIGH, luminance (Y) data into the TMC22x91 is forced to 0 IRE but sync pulses continue from the LUMA output.                                                                                                                                                                                                                                                                                                                     |

| 00  | 1   | CHRDIS | Chrominance input disable. When LOW (normal), burst and frame buffer data into the TMC22x91 are enabled. when HIGH, burst and frame buffer data are suppressed, enabling monochrome operation.                                                                                                                                                                                                                                                                                                                                              |

| 00  | 0   | HRESET | Software reset enable. SRESET is forced LOW when the RESET pin is taken LOW. State machines are reset and held. When HRESET is LOW, RESET may be taken HIGH at any time. The TMC22x91 is enabled and a new frame is begun with line 1, field 1 on the next PXCK after SRESET is set HIGH. The D/A converters are powered down while RESET is LOW. When HRESET is HIGH, a new frame is begun with line 1, field 1 on the next PXCK after RESET is taken HIGH. SRESET is ignored. The D/A converters remain active during the reset sequence. |

# Control Register Definitions (continued)

# Format Control Register (01)

| 7        | 6     | 5      | 4  | 3   | 2   | 1   | 0   |

|----------|-------|--------|----|-----|-----|-----|-----|

| Reserved | LCREN | RAMPEN | СВ | FOR | MAT | INM | ODE |

| Reg | Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01  | 7   |        | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 01  | 6   | LCREN  | (TMC22191) Layering Control Register enable. When LOW, the Layering Control Register is not available and Key Control Register functions are enabled. In this mode, the TMC22191 functions like the TMC22091. When HIGH, the Layering Control Register takes the place of the Key Control Register and enables the layering functions. Data loaded into the Key or Layering Control Registers will remain but have a different meaning if this bit is changed.                                                                                                                 |

| 01  | 5   | RAMPEN | Modulated ramp test. When LOW (normal), the TMC22x91 encodes and outputs video corresponding to input data. When RAMPEN and $\overline{\text{CB}}$ are both HIGH, an internally generated 40 IRE modulated ramp is produced, preempting input data.                                                                                                                                                                                                                                                                                                                            |

| 01  | 4   | CB     | Color bar test. When HIGH (normal), the TMC22x91 encodes and outputs video corresponding to input data. When $\overline{\text{CB}}$ , RAMPEN, and Format Control Register bit 0 are LOW, internally generated color bars are produced, preempting input data.                                                                                                                                                                                                                                                                                                                  |

| 01  | 3-2 | FORMAT | PD23-0 input format select. Two bits select RGB, GBR, or YCBCR input data. When bits 3 and 2 are:  0 0 the CLUT output is interpreted as RGB and is converted to YCBCR.  0 1 is reserved. Bits 3 and 2 must be 00 or 10 when the Layering Control Register is enabled (TMC22191).  1 0 the CLUT output is interpreted as GBR, and is converted to YCBCR.                                                                                                                                                                                                                       |

| 01  | 1-0 | INMODE | 1 1 the CLUT output is interpreted as YCBCR.  PD <sub>23-0</sub> input mode select. These two bits set up the TMC22x91 for either 444, 422, 15-bit, or 8-bit input modes.  0 0 24-bit/pixel GBR, RGB, or YCBCR444 data enters from PD <sub>23-0</sub> 0 1 YCBCR422 data enters from PD <sub>23-8</sub> ; CR and CB alternate from PD <sub>15-8</sub> 1 0 15-bit/pixel GBR or RGB data from PD <sub>14-0</sub> 1 1 8-bit/pixel color indexed data enters from PD <sub>7-0</sub> .  Bits 1 and 0 must be 00, 01, or 11 when the Layering Control Register is enabled (TMC22191). |

# Control Register Definitions (continued)

# Interface Control Register (02)

| 7      | 6    | 5   | 4   | 3    | 2     | 1      | 0     |

|--------|------|-----|-----|------|-------|--------|-------|

| VITSEN | SHCY | TBA | ASE | SOUT | FBDIS | PDCDIR | FLDLK |

| Reg | Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                         |

|-----|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02  | 7   | VITSEN | VITS lines enable. When LOW, all UBB lines in the vertical interval are black burst regardless of input data. When HIGH, all UBB lines in the vertical interval become UVV active video and are dependent upon input data.                                                                                                                                       |